Schéma de la carte d'interface

Voici la version du schéma pour le mode simulation, les entrées des composants ont été remplacées par des simulateurs d'état logique (soit 1, soit 0). Par ce schéma on peut comprendre facilement le rôle chaque composant. La version source du schéma permettant la simulation sous proteus est proposée dans les téléchargements du projet.

Le schéma est très simple, 3 74hc574 reçoivent un octet en provenance des sorties « data » du port parallèle, la broche « clock » de chaque circuit est reliée à une sortie différente du port parallèle, suivant quelle broche « clock » sera activée, un circuit basculera les données data dans sa mémoire (q0->q7) et les conservera jusqu’au prochain coup sur l’horloge. Nous pouvons ainsi contrôler 21 sorties.

Les entrées sont traitées par 2 74hc151. Suivant les données envoyées aux broches ABC de ces composants via 3 sorties du troisième circuits 74hc574 (d’où qu’il n’y a que 21 sorties au lieu de 24), la valeur d’une des entrées passera sur la broche Y et son inverse sur /Y. Les 2 Transistors BC547 permettent de faire passer les entrées du port parallèle à l’état 1 ou 0. Le circuit U4 est connecté sur la sortie inversée car il est connecté à une entrée inversée sur port parallèle. L’alimentation n’est pas dessinée dans le circuit mais bien comprise dans le circuit imprimé via un 7805.

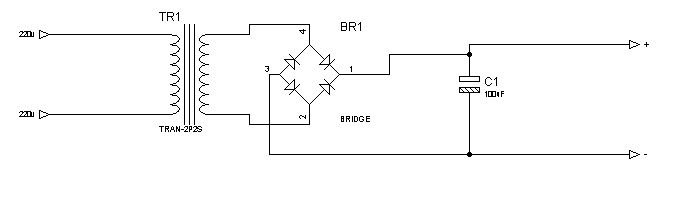

La carte peut-être alimentée par une pile 9V, ou par une alimentation externe, attention, dans le data-sheet du 7805 on remarque que la tension maximale imposable au borne du composant est de 36Volt... Il est donc pas question de lui imposé plus ou de le relier directement au 220Volt (Ce qui est tout à fait normale... surtout que celui-ci est en alternatif, mais je préfère prévenir...)